這項新技術使動態範圍擴大並降低了噪點,將避免在有明暗差(例如背光設置)的場景下曝光不足和過度曝光的問題,即使在光線不充足(例如室內、夜間)的場景下也能拍攝高品質低噪點的影像。Sony將通過雙層電晶體像素技術致力於實現更高品質的成像,例如智慧手機拍攝等。

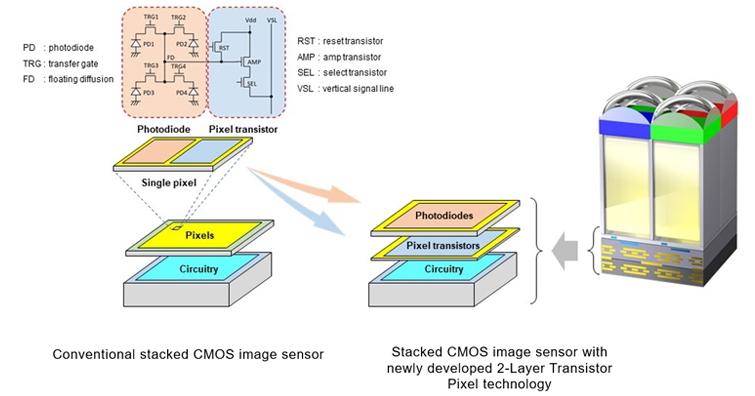

Sony已成功開發出全球首創*1的雙層電晶體像素堆疊式CMOS影像感測器技術。傳統CMOS影像感測器的光電二極體和像素電晶體分佈在同一基片,而Sony的新技術將光電二極體和像素電晶體分離在不同的基片層。與傳統影像感測器相比,這一全新的結構使飽和信號量*3約提升至原來的2倍*2,擴大了動態範圍並降低噪點,從而顯著提高成像性能。採用新技術的像素結構,無論是在當前還是更小的像素尺寸下,都能保持或是提升像素現有的特性。

*1: 截至2021年12月16日發佈時間。

*2: 基於公司之前的影像感測器和應用新技術的Sony背照式CMOS影像感測器之間特性的比較(換算為1um), 截至2021年12月16日發佈時間。

*3:單個像素的最大電子存儲容量。

Sony在2021年12月11日(星期六)開始的IEEE國際電子設備會議上宣佈了這一突破性技術。

堆疊式CMOS影像感測器結構

(傳統的)堆疊式CMOS影像感測器的堆疊式結構中,背照式像素組成的像素晶片堆疊在邏輯晶片之上,而信號處理電路構成了邏輯晶片。在像素晶片內,用於將光轉換為電信號的光電二極體和用於控制信號的像素電晶體在同一基片層並列。在這樣的結構限制下,如何實現飽和信號量的最大化,對實現高動態範圍、高影像品質的攝影具有重要作用。

Sony開發出的全新結構是堆疊式CMOS影像感測器技術的一項進步。Sony使用專有的堆疊技術,將光電二極體和像素電晶體封裝在分離的基片上,一個堆疊在另一個上面。

相比之下,在傳統的堆疊式CMOS影像感測器中,光電二極體和像素電晶體並排位於同一基片上。新的堆疊技術支援採用可以獨立優化光電二極體和像素電晶體層的架構,從而使飽和信號量相比於傳統影像感測器增加約一倍,進而擴大動態範圍。

此外,因為傳輸門 (TRG) 以外的像素電晶體,包括重定電晶體 (RST)、選擇電晶體 (SEL) 和放大電晶體 (AMP),都處於無光電二極體分佈這一層,所以放大電晶體(AMP)的尺寸可以增加。通過增加放大電晶體尺寸,Sony成功地大幅降低了夜間和其他昏暗場景下影像容易產生的噪點問題。

這項新技術使動態範圍擴大並降低了噪點,將避免在有明暗差(例如背光設置)的場景下曝光不足和過度曝光的問題,即使在光線不充足(例如室內、夜間)的場景下也能拍攝高品質低噪點的影像。

▲ 傳統的堆疊式影像感測器(左);採用新開發的雙層電晶體圖元技術的堆疊式CMOS影像感測器(右)

▲ 採用雙層電晶體像素技術的CMOS影像感測器的橫截面圖片。